The Control Unit is covered in Unit 03 of Computer Organization and Architecture. Topics covered include the instruction cycle, instruction pipelining, hardwired and microprogrammed control, interrupt handling, and input/output (I/O) activities. Students will have a good knowledge of the Control course’s role in computer architecture and how it helps to the efficient execution of programs by the conclusion of this course.

Dudes 🤔.. You want more useful details regarding this subject. Please keep in mind this as well. Important Questions For Computer Organization and Architecture: *Unit-01 *Unit-02 *Unit-03 *Unit-04 *Unit-05 *Short-Q/Ans *Question-Paper with solution 21-22

Q1. What is an instruction in the context of computer organization ? Explain the purpose of the various elements of an instruction with the help of a sample instruction format.

Ans. Instruction:

- 1. Instruction is a command to the processor to perform a given task on specified data.

- 2. An instruction is a binary pattern that has been specifically created and is based on the CPU’s architecture to carry out a particular task. The instruction set refers to the full collection of instructions. Instruction format:

Instruction has two parts opcode and operand,

- 1. The data to be operated on is referred to as the operand, and the action to be taken is referred to as the operation code (Opcode).

- 2. The operation’s input data and the output outcomes are both considered operands.

- 3. A computer must have instructions capable of performing four types of operations:

- a. Data transfers between the memory and the CPU registers.

- b. Arithmetic and logic operations on data.

- c. Program sequencing and control.

- d. I/O transfers.

- 4. An instruction’s main function is to indicate an operation for a CPU to perform as well as the set of operands or data that will be used in that action.

Example:

This instruction will multiply two operand A and B and result is stored in A.

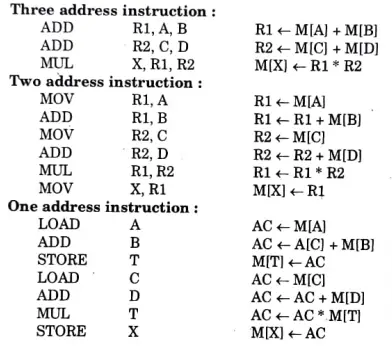

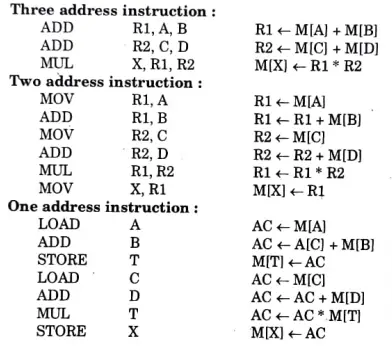

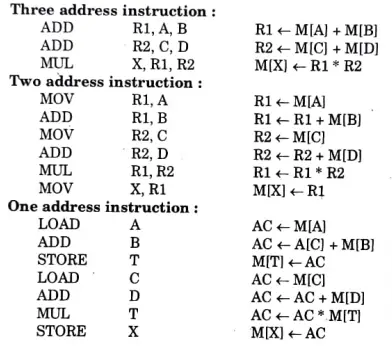

Q2. Evaluate the arithmetic statement X = (A +B)*(C + D) using a general register computer with three address, two address and one address instruction format a program to evaluate the expression.

Ans.

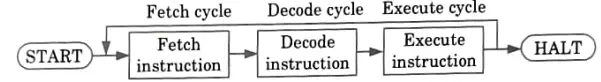

Q3. Explain all the phases of instruction cycle.

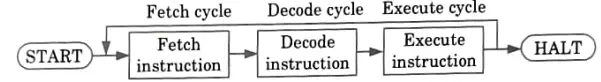

Ans. Instruction cycle:

- 1. Instruction cycle is a complete process of instruction execution.

- 2. It is a basic operational process of a computer.

- 3. It is the procedure a computer uses to obtain a programme instruction from memory, interpret the instruction to determine what actions to take, and then execute those actions.

The instruction cycle is divided into three sub cycles:

1. Fetch cycle: To fetch an opcode from a memory location following steps are performed:

- i. The address of the memory region where the opcode is stored is put on the address bus by the programme counter.

- ii. To allow the memory to send the opcode, the CPU provides the necessary memory control signals.

- iii. The opcode is put on the data bus and sent to the CPU after being stored in the memory location.

2. Decode cycle:

- i. The first thing to go into the Data Register (DR), or data/address buffer in the case of the Intel 8085, is the opcode that was just received from memory. After then, it is directed to the Instruction Register (IR).

- Ii. It travels from the instruction register to the CPU’s decoder circuitry.

- iii. The decoder circuitry decodes the opcode.

- iv. The CPU determines the action to be carried out after the opcode has been decoded, and execution then starts.

3. Execute cycle:

- i. In this cycle, function of the instruction is performed.

- ii. If the instruction involves arithmetic or logic, ALU is utilized.

Q4. Write the steps in fetching a word from memory. Differentiate between a branch instruction and call subroutine instruction.

Ans. Steps in fetching a word from memory are as follows:

Step 1: The CPU has to perform opcode fetch cycle and operand fetch cycle.

Step 2: The CPU receives the operation code necessary to retrieve a word from memory during the opcode fetch cycle.

Step 3: The operand fetch cycle is then started by the CPU.

Step 4: The address of the memory location where the data is saved is specified by the opcode.

Step5: The Address Register (AR), which is coupled to the address lines of the memory bus, receives the address of the required bit of information from the CPU. The address is therefore sent to the memory.

Step 6: When a read operation is required, the CPU triggers the memory’s read signal.

Step 7: As a.result, memory copies data from the addressed register on the data bus.

Step 8: The CPU then loads the data into the designated register after reading it from the data register.

Step 9: For this memory transfer, the signal Memory Functions Completed (MFC) is also employed as a control signal.

Step10: MFC is set to 1 by memory to signify that the specified location’s contents have been read and are now accessible via the data bus.

Difference:

| S. No. | Branch instruction | Subroutine instruction |

| 1. | A machine language or assembly language instruction is a branch instruction. | A control transfer instruction is a subroutine. |

| 2. | It is employed to alter the order in which instructions are executed. | It is used to call a subroutine. |

Q5. What is CISC ? Explain its characteristics.

Ans. 1. Computers with a full set of computer instructions that were intended to give necessary capabilities in the most effective manner are referred to as “CISC” (Complex Instruction Set Computers or Computing).

2. Complex instruction sets, variable instruction length encoding, and variable clock cycle execution are all features of CISC.

3. The CISC computer often requires less instructions to carry out the computation because there are so many different addressing mechanisms for operations and instructions.

4. Programs that are written for CISC architectures typically occupy less memory.

Characteristics of CISC:

1.Implementing the CISC machine’s performance is preferable if complex operations occur frequently.

2.To support multiple opcode types and operand addressing techniques, CISC frequently uses a variety of instruction formats.

3. CISC has many instruction formats.

4. The memory-based operands can be directly manipulated by CISC processors.

Q6. What is RISC ? Explain its various characteristics.

Ans. 1. Each instruction on a RISC (Reduced Instruction Set Computer) processor has a fixed length encoding, and each instruction is programmed to run in a single clock cycle.

2. With fewer instructions and a smaller instruction set that only supports a few addressing modes, RISC architecture focuses on executing more instructions in the same amount of time.

3. Although programmes created for RISC architectures often take up more memory, they can run faster on RISC processors due to their higher clock rates than they can on CISC processors.

RISC characteristics:

1. Simple instructions are used in RISC architecture.

2. A few simple data types are supported and helped by RISC, which also creates complicated data types.

3. Simple addressing modes and fixed-length instructions are used in RISC pipelining.

4. RISC permits any register to use in any context.

Important Question with solutions | AKTU Quantums | Syllabus | Short Questions

Computer Organization and Architecture Quantum PDF, Syllabus, Important Questions

| Label | Link |

|---|---|

| Subject Syllabus | Syllabus |

| Short Questions | Short-question |

| Important Unit-1 | Unit-1 |

| Important Unit-2 | Unit-2 |

| Important Unit-3 | Unit-3 |

| Important Unit-4 | Unit-4 |

| Important Unit-5 | Unit-5 |

| Question paper – 2021-22 | 2021-22 |

Computer Organization and Architecture Quantum PDF | AKTU Quantum PDF:

| Quantum Series | Links |

| Quantum -2022-23 | 2022-23 |

AKTU Important Links | Btech Syllabus

| Link Name | Links |

|---|---|

| Btech AKTU Circulars | Links |

| Btech AKTU Syllabus | Links |

| Btech AKTU Student Dashboard | Student Dashboard |

| AKTU RESULT (One VIew) | Student Result |