Are you looking for key computer memory questions for your AKTU B.Tech. course in Computer Organization and Architecture? This post will help you! To prepare for your tests, learn about memory structure, addressing modes, and data transmission strategies. Get your hands on some of the most significant questions and easily pass your examinations.

Dudes 🤔.. You want more useful details regarding this subject. Please keep in mind this as well. Important Questions For Computer Organization and Architecture: *Unit-01 *Unit-02 *Unit-03 *Unit-04 *Unit-05 *Short-Q/Ans *Question-Paper with solution 21-22

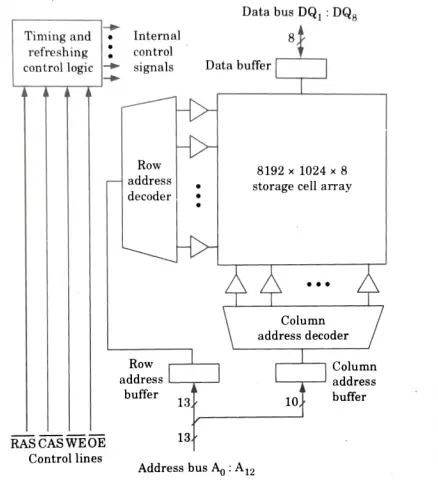

Q1. Give the structure of commercial 8M x 8 bit DRAM chip.

Ans.

Q2. How main memory is useful in computer system ? Explain the memory address map of RAM and ROM.

Ans. Main memory is useful in computer system:

- 1. A computer system’s main memory is located in the centre.

- 2. Through an I/O processor, it can communicate both directly with the CPU and with auxiliary memory devices.

- 3. It is relatively large and fast.

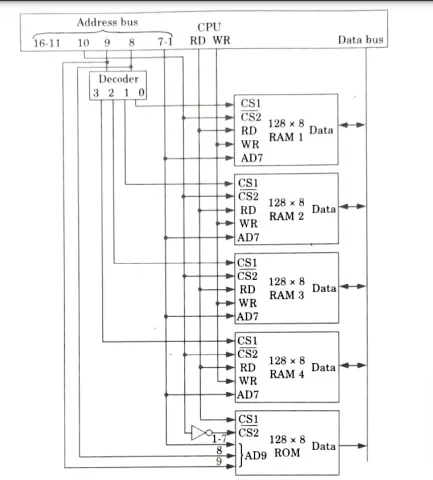

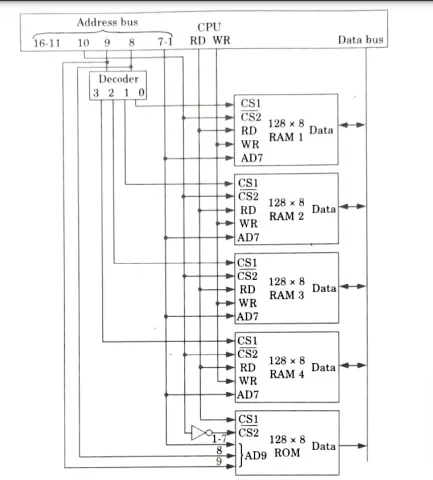

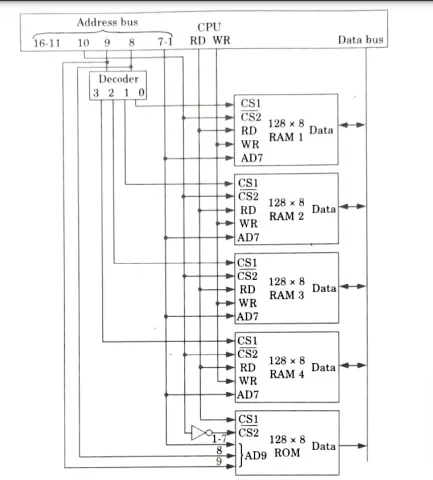

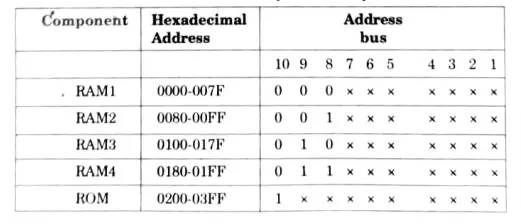

Memory address map of RAM and ROM:

- 1. A memory address map is a visual depiction of the address space allotted to the system’s chips.

- 2. Assume that a computer system needs 512 bytes of RAM and 512 bytes of ROM in order to illustrate with a specific example.

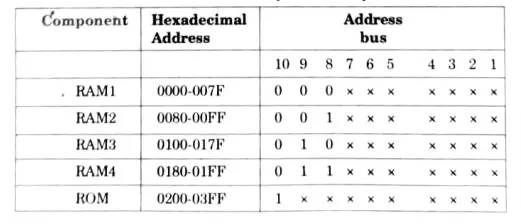

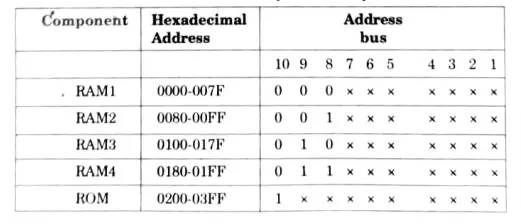

- 3. Fig. lists the RAM and ROM chips that will be used. Table displays the memory address map for this configuration.

- 4. Whether a RAM or ROM chip is utilized is indicated in the component column. Each chip is given a set of addresses with hexadecimal equivalents according to the hexadecimal address column. The third column has a list of the address bus routes.

- 5. Through bus line 10, the choice between RAM and ROM is made. When the bit in this line is 0, the RAMs are chosen, and when the bit is 1, the ROM is chosen.

Memory address map

- 6. The lines that must be connected to each chip’s address inputs are indicated by an x under the address bus lines.

- 7 The RAM chips have 128 bytes and need seven address lines.

- 8. The ROM chip has 512 bytes and need 9 address lines.

- 9. Four RAM chips must now be distinguished from one another by being given unique addresses.

Q3. A computer uses RAM chips of 1024*1 capacity.

i. How many chips are needed and how should their address lines be connected to provide a memory capacity of 1024*8 ?

ii. How many chips are needed to provide a memory capacity of 16 KB ? Explain in words how the chips are to be connected to AKTU 2018-16, Marks 10 the address bus.

Ans. i. Available size of RAM chips = 1024 x 1

Required memory capacity = 1024 bytes

= 1024 x 8

So, 8 chips are needed with address line connected in parallel.

ii. To provide a memory capacity of 16K bytes, chips required are 16 x8 = 128 chips

Number of address line for 16 K = 14 (16 K= 214)

So, 14 lines to specify chip address.

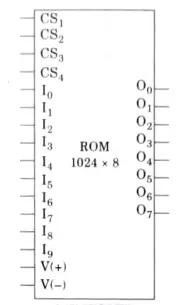

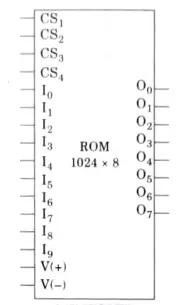

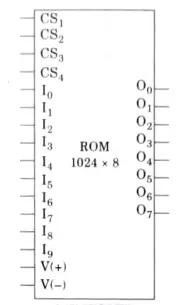

Q4. A ROM chip of 1024*8 has four select inputs and operates from a 5 volt power supply. How many pins are needed for the IC package ? Draw a block diagram and label all input and output AKTU 2015-16, Marks 10 terminals in the ROM.

Ans. Size of ROM Chip = 1024 x 8

Number of input = 10 pin [210 = 1024]

Number of output = 8 pin

Number of chip select = 4 pin

Power = 2 pin

Total 24 pins are required.

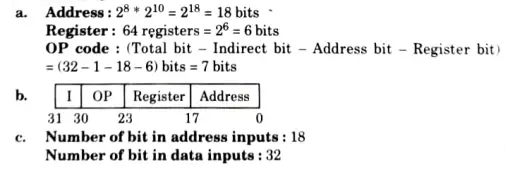

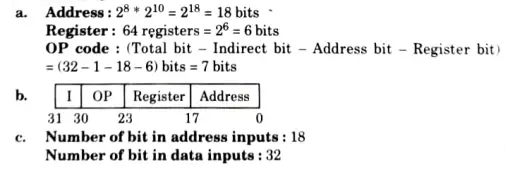

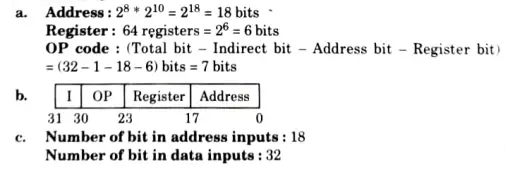

Q5. A computer uses a memory unit with 256 K words of 32 bits each. A binary instruction code is stored in one word of memory. The instruction has four parts: an indirect bit, an operation code, a register code part to specific one of 64 register and an address part.

i. How many bits are there in the operation code, the register code part and the address part ?

ii. Draw the instruction word format and indicate the number of bits in each part.

iii. How many bits are there in the data and address inputs of the memory?

Ans.

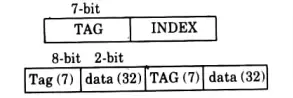

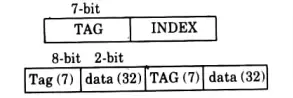

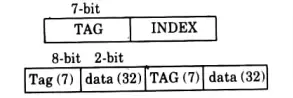

Q6.A two way set associative cache memory uses blocks of 4 words. The cache can accommodate a total of 2048 words from memory. The main memory size is 128 K x 32.

I. Formulate all pertinent information required to construct the cache memory.

ii. What is the size of the cache memory?

Ans. i. Main memory size = 128K x 32 = 217

Cache size 2048 words

Set size of 2 cache can accommodate = 2048/2 = 1024 words of cache

Block size = 4 words

ii.

Size of cache memory = 1024 x 2(7+ 32) = 1024 x 78

Important Question with solutions | AKTU Quantums | Syllabus | Short Questions

Computer Organization and Architecture Quantum PDF, Syllabus, Important Questions

| Label | Link |

|---|---|

| Subject Syllabus | Syllabus |

| Short Questions | Short-question |

| Important Unit-1 | Unit-1 |

| Important Unit-2 | Unit-2 |

| Important Unit-3 | Unit-3 |

| Important Unit-4 | Unit-4 |

| Important Unit-5 | Unit-5 |

| Question paper – 2021-22 | 2021-22 |

Computer Organization and Architecture Quantum PDF | AKTU Quantum PDF:

| Quantum Series | Links |

| Quantum -2022-23 | 2022-23 |

AKTU Important Links | Btech Syllabus

| Link Name | Links |

|---|---|

| Btech AKTU Circulars | Links |

| Btech AKTU Syllabus | Links |

| Btech AKTU Student Dashboard | Student Dashboard |

| AKTU RESULT (One VIew) | Student Result |

1 thought on “Important Question Unit 04 Memory -Computer Organization and Architecture”