The topic of Input/Output (I/O) systems, their components, and their interfaces with the computer system is covered in Unit 05 – Input/Output in Computer Organization and Architecture for AKTU B.Tech. This subject also focuses on the design and performance analysis of I/O systems.

Dudes 🤔.. You want more useful details regarding this subject. Please keep in mind this as well. Important Questions For Computer Organization and Architecture: *Unit-01 *Unit-02 *Unit-03 *Unit-04 *Unit-05 *Short-Q/Ans *Question-Paper with solution 21-22

Q1. Why input-output interface is required ? Describe in detail.

Ans. I/O interface provides a method of transferring information between internal storage and external I/O devices.

The major requirements for an I/O module can be given a:

1. Processor communication : This involves the following tasks:

a. Exchange of data between processor and VO module.

b. Command decoding: The I/O module for a disk drive may accept the following commands from the processor READ SECTOR, WRITE SECTOR, SEEK track, etc.

c. Status reporting: The gadget must be able to inform the processor of its state. For instance, a busy or ready disc drive.

d. Status reporting may also involve reporting various errors.

e. Address recognition: The I/O module must be able to identify the specific address assigned to each I/O device.

2. Device communication : The I /O module is able to perform device communication such as status reporting.

3. Control and timing: Between internal resources (such the processor and memory) and external devices, the I/O module may coordinate the data flow..

4. Data buffering :

a. This is required because to the speed difference in data flow between the CPU, memory, and external devices.

b. An I/O module receives data from the main memory in short bursts.

c. The I/O module buffers the data before sending it to the peripheral device at its rate.

5. Error detection:

a. The VO module is able to detect errors and report them to the processor.

b. Mechanical faults, like a paper jam in a printer, or variations in the bit pattern of sent data may be the cause of these errors. Using parity bits is a typical technique for identifying such problems.

Q2. Write a short note on interrupts.

Ans. Interrupt: When the CPU is prepared to transfer or receive data from the memory, the I/O interface will signal the CPU with an interrupt.

Identifying the source of an interrupt:

Two methods are available to determine the interrupting device:

a. Polled interrupts:

1. The microprocessor will run a programme that causes it to poll each of the devices in turn when it receives an interrupt request.

2. Devices have a status register containing one or more interrupt request bits.

3. A device’s interrupt flag bit will be set if it initiated the interrupt.

4. The item will then be serviced after choosing the proper maintenance procedure.

5. If there are multiple devices that can interrupt a process, polling may not be very effective.

6. This technique simply employs software techniques to recognise an interrupting device.

b. Vectored interrupts:

1. This is the method used in modern computers.

2. Since additional hardware is needed, it is also known as hardware identification.

3. The CPU can address the proper interrupt handler by using a vector, which is designated by an interrupt number ranging from 0 to 255.

4. To find a vector address, multiply a vector number by four.

Q3. Explain the sequence that takes place when an interrupt AKTU 2015-16, Marks 10 occurs.

Ans. When an interrupt occurs, sequence of following six steps takes place:

1. Interrupt recognition:

a. The activation of an interrupt request line or an internal mechanism causes the interrupt recognition to be recognised by the processor of an interrupt request.

b. The processor can identify the device or CPU component that made the request in this stage.

2 Status saving:

a. Making the interrupt sequence visible to the interrupted process is the aim of this phase.

b. So that they can be restored when the interrupt service routine is finished, the processor saves the flags and registers that the interrupt service procedure may change.

3. Interrupt masking:

a. All interrupts are blocked during the first few steps of the sequence so that nothing else can be processed before the processor state is recorded.

b. The mask is then set to accept interrupts of higher priority.

4. Interrupt acknowledgment:

a. The interrupting device must eventually be given the opportunity to a. do its task by the processor acknowledging the interrupt as it is being handled.

b. One method is to designate an external signal line as an interrupt acknowledgement line.

5. Interrupt service routine:

a. At this point, the processor initiates the interrupt service routine.

b. Depending on the system architecture, a number of methods can be used to determine the routine’s address.

c. The simplest is found in the polling method, in which one routine polls each device to find which one interrupted.

6. Restoration and return:

a. The processor restores all the registers and flags that were saved at the start of the interrupt procedure when the interrupt service routine has finished processing and restored all the registers it has altered.

b. If everything goes according to plan, the processor should be in the same condition as it was before the interrupt was acknowledged.

Q4. How interrupts are classified ?

Ans. Basically the interrupts can be classified in the following three ways:

1. Hardware and software interrupts:

a. Hardware interruptions are those that an external piece of hardware causes by sending the proper signal to the CPU’s interrupt pin.

b. The interruptions in the software are commands. These instructions are placed into the programme at the desired spot. If a software interrupt instruction is detected while running a programme, the CPU starts an interrupt.

2. Vectored and non-vectored interrupts:

a. The interrupt is referred to as a vectored interrupt when the CPU accepts an interrupt signal and automatically branches the programme control to a particular address (known as a vector address).

b. The interrupting device must provide the address of the interrupt service routine (ISR) that will be run in response to the interrupt in non-vectored interrupts.

3. Maskable and non-maskable interrupts:

a. Maskable interrupts are interrupt requests that the CPU has the option of accepting or rejecting.

b. Non-maskable interrupts are those whose requests must be unequivocally granted by the CPU.

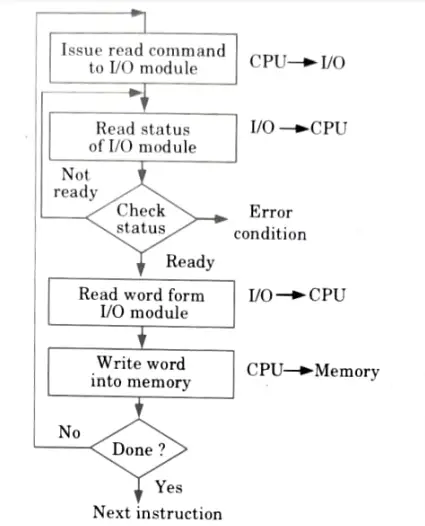

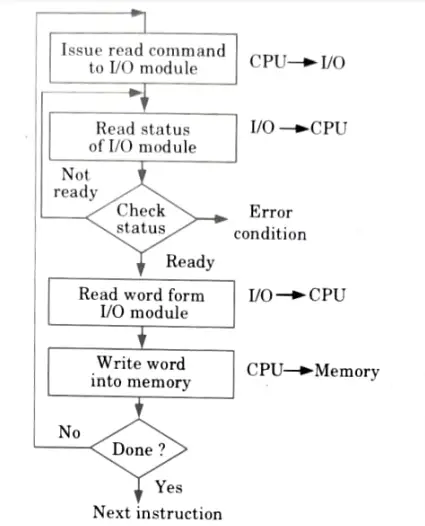

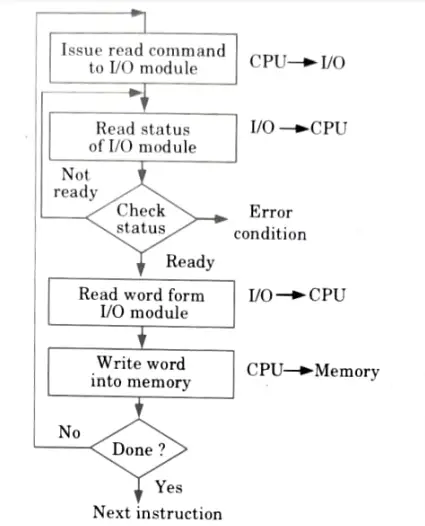

Q5. Discuss the programmed I/O method for controlling input-output operations.

Ans. Programmed I/O:

- 1. When the CPU is running a programme and has to carry out an I/O instruction, it sends a command to the relevant I/O module in order to carry out that instruction.

- 2.When using programmed I/O, the I/O module does the desired operation and then sets the relevant bits in the I/O status register.

- 3. The I/O module takes no further action to alert the CPU.

- 4. It does not interrupt the CPU.

- 5. Therefore, it is the CPU’s obligation to periodically monitor the I/O module’s state until it determines that the operation is finished.

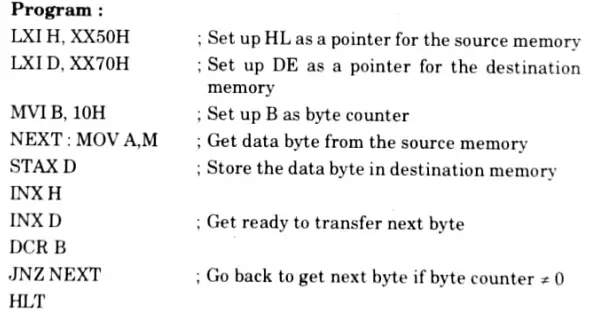

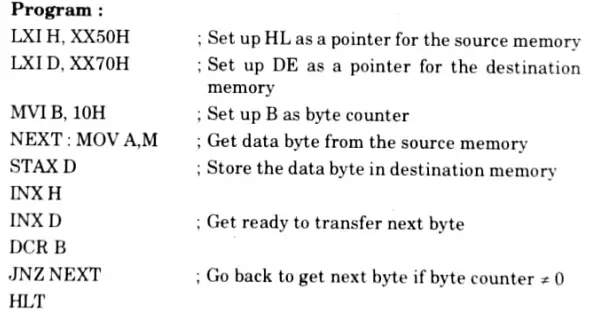

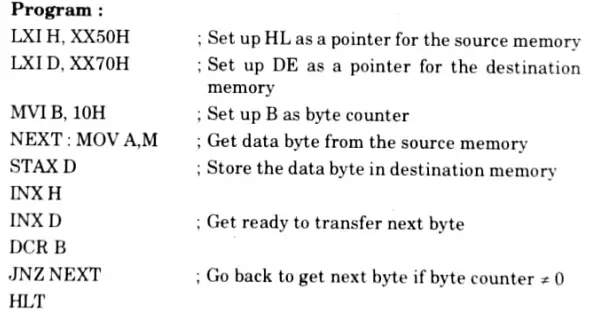

Q6. Describe the subroutine. Write a program which move the block of data.

Ans. Subroutine:

- 1. A subroutine is a collection of regular instructions that can be utilized repeatedly within a programme.

- 2. A subroutine is a standalone set of instructions that completes a specific task.

- 3. A branch is executed to the beginning of the procedure each time it is utilized in the program’s main body.

- 4. Following the execution of the subroutine, a branch is made back to the main programme.

- 5. A branch can be made to the subroutine from any part of the main program.

- 6. All computers include additional instructions to make subroutine entrance and return easier because it is so frequent to branch to a subroutine and then return to the main programme.

Important Question with solutions | AKTU Quantums | Syllabus | Short Questions

Computer Organization and Architecture Quantum PDF, Syllabus, Important Questions

| Label | Link |

|---|---|

| Subject Syllabus | Syllabus |

| Short Questions | Short-question |

| Important Unit-1 | Unit-1 |

| Important Unit-2 | Unit-2 |

| Important Unit-3 | Unit-3 |

| Important Unit-4 | Unit-4 |

| Important Unit-5 | Unit-5 |

| Question paper – 2021-22 | 2021-22 |

Computer Organization and Architecture Quantum PDF | AKTU Quantum PDF:

| Quantum Series | Links |

| Quantum -2022-23 | 2022-23 |

AKTU Important Links | Btech Syllabus

| Link Name | Links |

|---|---|

| Btech AKTU Circulars | Links |

| Btech AKTU Syllabus | Links |

| Btech AKTU Student Dashboard | Student Dashboard |

| AKTU RESULT (One VIew) | Student Result |